文章链接:https://www.nature.com/articles/s41467-021-26230-x

这篇文章的工作是近期Nature上发表文章2025,Nature——二维半导体技术突破:5,900个MoS₂晶体管实现32位RISC-V微处理器的基础,分享出来跟大家一起学习。

研究亮点

1.机器学习辅助工艺参数优化

o通过利用机器学习(ML)算法对关键工艺参数进行评估,显著提升了MoS₂顶栅FET的性能,如迁移率、阈值电压和亚阈值摆幅等。这种方法不仅提高了器件均一性,还为工艺稳定性提供了量化依据。

2.晶圆级集成的突破

o研究实现了基于二维MoS₂的晶圆级功能电路制造,涵盖了数字、模拟、以及光探测电路模块,并成功构建了标准单元库和实际功能模块(例如4位全加器)。这标志着二维半导体技术向工业标准化与大规模集成迈出了重要一步。

3.高精度建模与协同设计

o采用了62级SPICE模型来刻画MoS₂ FET的电学行为,并将其用于整个电路的仿真与设计。工艺与电路设计的协同优化,证明了以数据驱动的模型能够在柔性电路制造中发挥关键作用。

4.工业标准设计流程的实现

o在整个器件与集成系统的制备过程中,研究严格遵循行业标准设计流程,展示了二维半导体器件不仅具备实验室研究价值,而且具备向大规模工业应用转化的可能性。

可延伸的研究方向

1.复杂功能模块和系统化应用

o在现有标准单元库基础上,构建更复杂的逻辑电路、混合信号系统乃至系统级集成电路(SoC),为物联网、可穿戴电子、医疗健康监测等领域提供低功耗、高性能的解决方案。

2.柔性与可伸缩性集成探索

o结合二维材料的机械柔性特点,开发柔性、可拉伸的集成电路,探索在新型智能可穿戴设备和柔性显示器中的应用,同时研究柔性基底对器件电气性能的影响,并通过工艺优化进一步提高器件的可伸缩性。

摘要

在图灵式石墨烯开创性研究的推动下,二维层状材料(2DLMs)家族受到研究者近十余年的关注,并展现了诸多诱人的功能。然而,目前高质量生长及电路级集成方面仍面临挑战,现有研究成果与工业标准尚有较大差距。本文通过利用机器学习(ML)算法评估影响MoS₂顶栅场效应晶体管(FETs)电学特性的关键工艺参数,克服了上述难题。接着,结合网格搜索,采用机器学习指导晶圆级制造工艺,对器件的迁移率、阈值电压和亚阈值摆幅等性能进行协同优化。研究团队实现了对MoS₂ FET的62级SPICE建模,并基于该模型构建了功能性数字、模拟及光电探测电路。最后,利用符合工业标准的设计流程与工艺,成功展示了晶圆级测试的FET阵列以及一个4位全加器。所有这些结果均从实验上验证了机器学习辅助制程优化在超越硅基电子材料领域的应用潜力。

研究背景和主要内容

二维 (2D) 半导体具有从主流逻辑和模拟电路到柔性电子产品的潜在应用。半导体过渡金属二硫属化物( TMD ) 是一类

具有多功能能带结构的2D半导体,其中 MoS2是研究最广泛的TMD 代表。具有无悬挂键界面和低平面介电常数的原子级薄通道可确保在极其微小的器件中实现高载流子迁移率,并可对短沟道效应 (SCE)进行稳健控制。虽然2DLM 的固有优势在超摩尔电子应用方面前景光明,但要满足大规模电路和系统级应用的严格要求仍然具有挑战性,其中主要挑战是晶圆级材料合成和器件加工。最近,全球对化学气相沉积 ( CVD )和金属有机 CVD 合成的研究努力已经能够获得大面积的半导体 TMD 薄膜。虽然令人满意的晶体质量和大规模均匀性仍然需要进一步改进合成技术,但目前可用的晶圆级TMD薄膜实际上足以制造大规模电路。

为了实现基于二维半导体的复杂级联电路,电压匹配和高噪声容限也非常重要,这就需要精确控制场效应晶体管(FET)的阈值电压( VT )。到目前为止,已经报道了一个由115个采用先栅极技术制造的MoS2 FET组成的功能电路。然而,这种先栅极技术需要更复杂的薄膜转移工艺和额外的接触孔形成步骤,这不仅会给MoS 2

薄膜带来缺陷,而且会大大降低晶圆级制造的产量和可重复性。此外,从实际角度来看,具有高k介电层的顶栅(TG)结构FET(即传统的后栅极技术)对于独立栅极控制和电路级集成是必需的。因此,大规模电路需要更加重视TG-FET制造优化,以实现晶圆级的均匀性和可重复性。然而,二维半导体的超薄特性使其对外部环境和制造工艺极其敏感,尤其是二维半导体的顶部界面。在TG-FET制造过程中,所有单独的工艺步骤彼此高度耦合,因为任何后续的工艺步骤都会影响之前的工艺步骤,这使得二维半导体的工艺优化比Si和Ge等体半导体更加复杂。

本研究旨在实现2英寸MoS2晶圆的批量生产,利用机器学习(ML)算法分析实验数据并评估对二维场效应晶体管(FET)电学特性有显著影响的各种关键工艺参数,从而优化采用ML引导的后栅极工艺制造的增强型场效应晶体管(FET)的电学性能。通过测量电学数据进行校准,进行器件建模,以指导基础数字、模拟和光电电路的设计。通过使用行业标准设计流程和工艺进行晶圆级加工,我们的工作证明了使用ML优化新兴材料器件工艺的可行性,并缩短了从基础研究到实际应用的学习周期。

机器学习辅助的共同优化

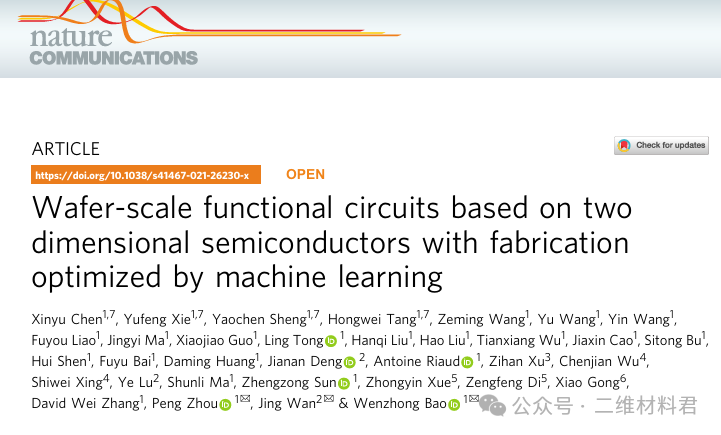

图 1:构建 MoS2 2D-FET 的全局图。a 通过 CVD 实现晶圆级 MoS2均匀生长的演示,包括材料生长设备示意图、一批均匀覆盖 MoS2的 2 英寸晶圆级蓝宝石衬底、一块均匀覆盖 MoS2并标有拉曼测试点的 2 英寸蓝宝石晶圆,以及上图中标记的不同位置的拉曼映射光谱。b具有TG (顶栅)和全局 BG(底栅)的 MoS2 FET 的示意横截面。对影响器件性能的各种界面因素进行了分类,包括在 MoS2和高 k 电介质之间插入种子层(SL) (在本工作中,SL 沉积在整个沟道区域上)、TG 和高 k 电介质之间的界面以及 MoS2和接触金属之间的界面。c

晶体管性能参数与集成电路性能极限关系示意图,其中µ、V T、I on / I off和 SS 分别代表迁移率、阈值电压、电流开/关比和亚阈值摆幅。d从材料合成到工业级电路设计、制造和测试的工艺流程和反馈优化图。

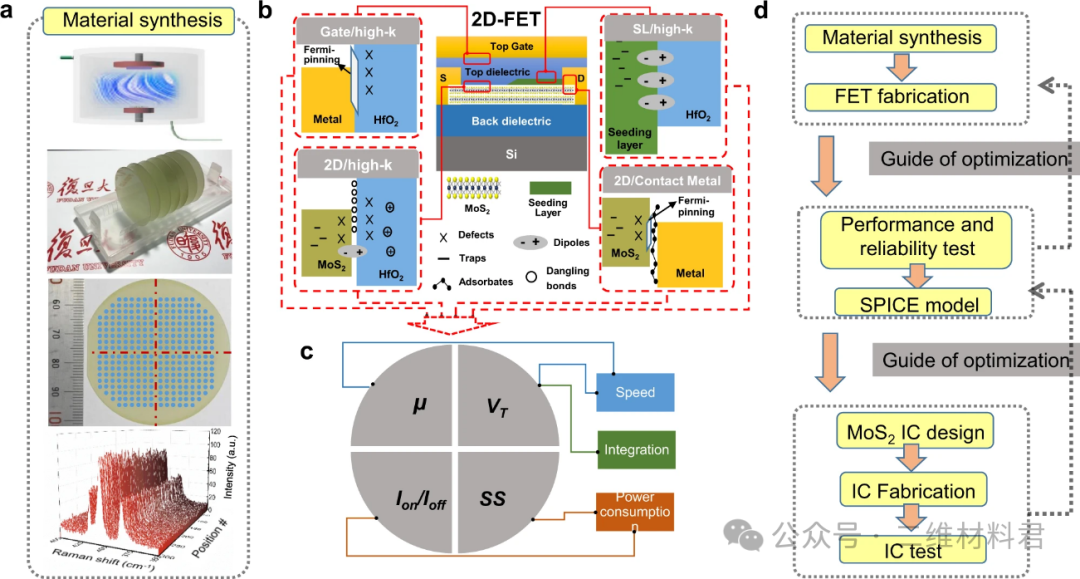

图 2:机器学习辅助优化 MoS2器件流程。a制造 TG MoS2 FET的工艺流程。每个步骤中的变化以蓝色标记。b基于决策树算法的集成学习 (EL) 的图形表示。在创建决策树期间提取每个处理步骤的重要性。c基于随机森林回归的 μ 和V T处理步骤的重要性,其中 S/D、SL 和 TG 代表源/漏接触、种子层和顶栅。d基于 ML 的协同优化过程图。经过 EL 训练后,分数预测器可以使用网格搜索方法预测所有处理组合的整体设备性能。e所有可能的处理组合的排名。高分组合可供设备制造参考。f μ – V T图总结了500 多个 MoS2 TG-FET。每种颜色对应一种工艺配方。红色星号是红色箭头指向的e中工艺配方的结果。橙色、绿色和蓝色点分别代表正文中讨论的控制实验所制造的三批器件。g为单晶圆上60个MoS2

TG-FET在V DS = 0.5 V时的转移特性 (线性和对数坐标)。插图显示了Y函数计算的迁移率(上图)和阈值电压(下图)统计数据的直方图和高斯拟合结果(红色实线)。

图 2a示意性地显示了制造 MoS2 TG-FET的完整过程(有关详细的处理步骤,另请参见补充说明 2)。在流程结束时测量 FET 性能。集成学习 (EL) 是一种监督式 ML 方法,其中聚合多种学习算法以实现更准确的预测,因为它可以有效地对不平衡数据进行分类(详细信息请参见补充说明 3)。决策树方法被用作弱分类器,因为它可以有效地处理离散数据(图 2b)。使用专门设计的工艺流程在 40 多个不同的晶圆上制造了 560 多个 MoS2 -FET,以提供全面的数据库。我们首先关注两个器件性能参数μ和V T,因为μ与操作速度直接相关,而V T对于制造增强型 FET 至关重要。可以使用一个优选参数(μ

或V T)作为 EL 分析的排序标准来确定每个处理步骤的重要性(图 2c)。根据物理分析,生成的结果是合理的,因为V T主要受 TG 结构(金属功函数和沉积栅极电介质中的电荷杂质/偶极子)的影响。同时,通过 Y 函数法提取迁移率μ,这取决于界面散射和接触电阻等多种因素。ML 分析表明,TG 电极金属化也成为一个必不可少的步骤,这是出乎意料的(详情见补充说明 7)。根据各种功能的要求,可以通过为每个参数乘以一个加权因子来综合考虑μ、V T和其他性能参数。

然后,我们证明 ML 也可用于共同优化所有工艺步骤,如图 2d所示。经过 EL 训练后,分数预测器可以预测特定处理组合(即一种工艺配方)的结果。然后使用网格搜索方法对所有可能的工艺配方进行排序,如图 2e所示。为了证明这一点,我们制造了 500 多个 MoS2 FET,这些 FET 总结在图 2f中的μ – V T图中。每种颜色对应一种工艺配方制造的 FET。大多数配方都是根据逐步优化的人为经验设计的

(详情见补充说明 4-9 )。例如,一种配方提供高μ值(橙色圆圈),另一种配方提供正VT (蓝色圆圈)。然而,混合两种配方(绿色圆圈)不能同时保证高μ和正V T,主要是由于不同处理步骤之间的串扰(详细讨论见补充说明 9)。因此,多个步骤的组合与每个优化并不一定能产生最佳器件。然后,我们 根据排序结果的建议( 图2e中的红色箭头)制造了一批器件(图2f中的红色星号)。该配方(处理细节,参见补充说明 9)也产生了平均约75cm2 /V∙s的μ和2.1V的V T,以及对于大规模电路很重要的高晶圆级均匀性,如图 2g所示(参见补充说明 10中的更多电气特性)。在未来,器件物理学仍然是必要的,以深入了解每个方面以进行进一步的优化。然而,详细的物理解释不是这项工作的重点。

因此,与传统的实验设计(DoE)相比,我们的机器学习辅助方法可以有效减少复杂的协同优化研究工作量。本文中,机器学习算法在MoS2 TG-FET优化中的应用只是一个案例研究,其缩短器件优化学习周期的能力可以方便地扩展到其他新兴电子材料和新型器件。

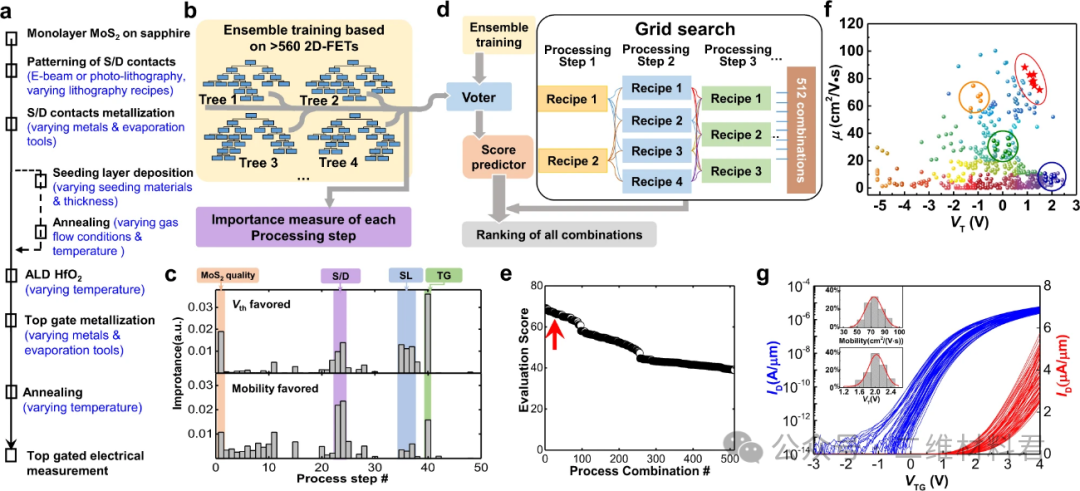

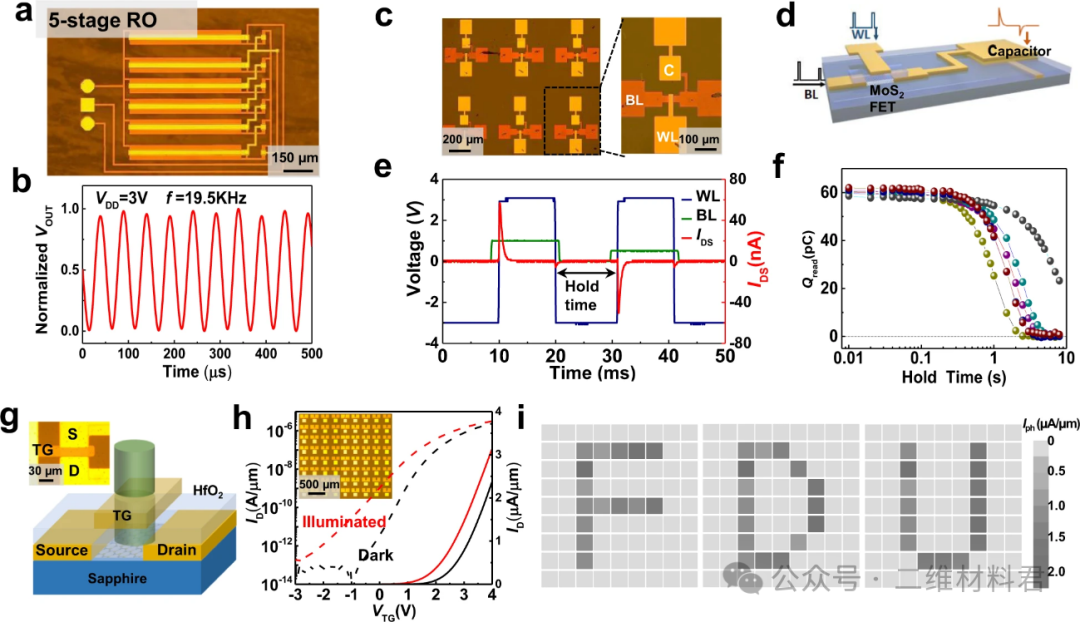

图 3:基于 MoS 2 TG-FET 的逻辑电路。a、b为 MoS2 TG-FET的转移和输出特性的实验数据(圆点)和模拟(线) , c、d 为带有 M1 和 M2 FET 的 MoS2反相器的电压传输曲线 (VTC) 。c中的插图为 MoS2伪 NMOS 反相器的示意图。c 中使用几何参数R = (W/L) M1 /(W/L) M2来调整 VTC 曲线的开关点, d中则采用了不同的方法,即独立调整M1 的V T。e为 MoS2下降沿触发 D 触发器 (DFF) 电路的光学显微镜图像,f为相应的实验结果。上面两个波形为电压摆幅为 0–3 V 的输入,下面的图形为测得的输出。g为1 位 MoS2全加器的光学显微镜图像,h为相应的实验结果。和的输出信号(S

)和进位输出(C o)以灰色阴影区域区分。

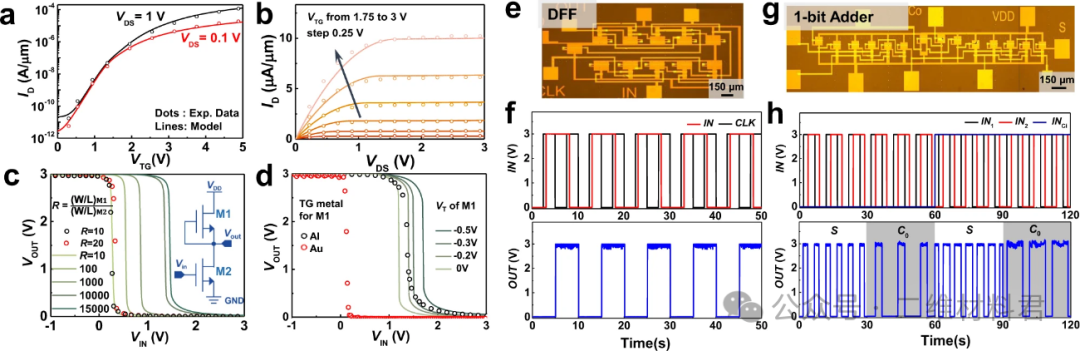

图 4:基于 MoS2 TG-FET 的模拟、存储器和光电电路。a为 5 级环形振荡器的光学显微镜图像,b为V DD = 3 V时 19.5 kHz 下的相应输出特性。c MoS2存储单元阵列的光学显微镜图像。右侧放大显示了 1T-1C 动态存储器电路的详细结构,其示意图如d所示。e , 1T-1C 单元中的写入和读取操作。WL,BL 和I DS表示写入线,位线和工作电流。f计算了五种不同器件的电容器中存储的电荷随保持时间的变化。g具有 10 nm 厚 Au顶栅的MoS2光电晶体管的示意图,h显示在 V DS = 0.5 V 时有和无照明的传输特性。g ,h中的插图 分别是 MoS2光电晶体管及其大规模阵列的光学显微镜图像。i 9 × 9 MoS

2 FET 阵列的光电流映射。光电流是通过使用显微镜聚焦的白光束扫描阵列产生的。

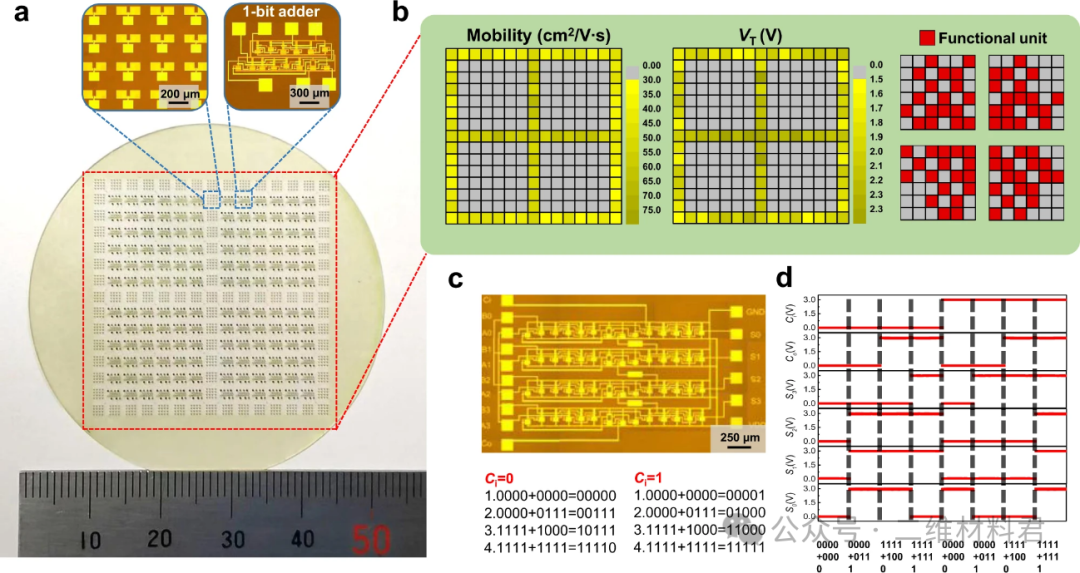

图 5:由 MoS2 FET构建的晶圆级集成电路。a 2英寸MoS2晶圆照片,中心区域为1位全加器阵列作为功能电路,周围区域为MoS2 TG-FET阵列作为监控器件。所有MoS2 TG-FET和1位全加器均在红色虚线方块内制作。蓝色虚线框的放大图为相应的MoS2 TG-FET和1位全加器阵列的光学显微镜图像。b晶圆迁移率图(左)和VT统计图(中),提取自周围区域的器件。黄色比例尺显示迁移率和VT值。每个块的颜色标度代表16个FET的平均值,整个晶圆有81个块。右图显示了1位全加器电路阵列的产量。红色和灰色方块分别表示工作电路和非工作电路的比例。c 4位全加器的光学显微镜图像,下方是逻辑组合的真值表。d在V DD = 3 V时对 4 位全加器进行功能测量。 使用一系列输入组合 (A, B) 按以下顺序测试 4 位全加器:(0000 + 0000, 0000 + 0111, 1111 + 1000, 1111 + 1111),其中C i = 0 和C i

= 1。y 轴分别是进位输入 ( C i ) 和进位输出 ( C o ) 的电压,以及和0 ( S 0 )、和1 ( S 1 )、和2 ( S 2 )、和3 ( S 3 )的输出电压。

讨论

目前,晶圆级 MoS2和其他 2D 半导体的合成正在快速发展,为制造 FET 和 IC 提供了更多的候选材料。即使对于本工作中研究的 MoS2薄膜本身,也可以进一步优化合成方法以改变晶粒尺寸、结晶度、缺陷密度等,这些都会影响 MoS 2 FET 的整体性能。这是学术研究人员选择不花大力气优化特定 2D 半导体的制造工艺的主要原因之一。因此,我们的研究成果可以扩展到其他 2D 半导体和新兴新材料,以减轻他们的器件优化负担并缩短学习周期。当然,这种加速方法更适合于器件优化的初始阶段。一旦达到一定水平,仍然需要对器件物理的理解以进一步改进。